## Essai et déverminage des circuits intégrés complexes : possibilités et méthodologie

Autor(en): Birolini, A.

Objekttyp: Article

Zeitschrift: Bulletin des Schweizerischen Elektrotechnischen Vereins, des

Verbandes Schweizerischer Elektrizitätsunternehmen = Bulletin de

l'Association Suisse des Electriciens, de l'Association des

Entreprises électriques suisses

Band (Jahr): 75 (1984)

Heft 1

PDF erstellt am: **24.05.2024**

Persistenter Link: https://doi.org/10.5169/seals-904327

#### Nutzungsbedingungen

Die ETH-Bibliothek ist Anbieterin der digitalisierten Zeitschriften. Sie besitzt keine Urheberrechte an den Inhalten der Zeitschriften. Die Rechte liegen in der Regel bei den Herausgebern. Die auf der Plattform e-periodica veröffentlichten Dokumente stehen für nicht-kommerzielle Zwecke in Lehre und Forschung sowie für die private Nutzung frei zur Verfügung. Einzelne Dateien oder Ausdrucke aus diesem Angebot können zusammen mit diesen Nutzungsbedingungen und den korrekten Herkunftsbezeichnungen weitergegeben werden.

Das Veröffentlichen von Bildern in Print- und Online-Publikationen ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. Die systematische Speicherung von Teilen des elektronischen Angebots auf anderen Servern bedarf ebenfalls des schriftlichen Einverständnisses der Rechteinhaber.

#### Haftungsausschluss

Alle Angaben erfolgen ohne Gewähr für Vollständigkeit oder Richtigkeit. Es wird keine Haftung übernommen für Schäden durch die Verwendung von Informationen aus diesem Online-Angebot oder durch das Fehlen von Informationen. Dies gilt auch für Inhalte Dritter, die über dieses Angebot zugänglich sind.

Ein Dienst der *ETH-Bibliothek* ETH Zürich, Rämistrasse 101, 8092 Zürich, Schweiz, www.library.ethz.ch

# Essai et déverminage des circuits intégrés complexes – possibilités et méthodologie

A. Birolini

L'essai a pour but de vérifier le niveau de qualité et de fiabilité d'un circuit intégré donné. Il peut aller d'un simple contrôle d'entrée jusqu'à l'essai de qualification comprenant une caractérisation, des essais d'environnement et de fiabilité et une analyse des défaillances. Le but du déverminage, par contre, est de provoquer la défaillance de tous les composants faibles contenus dans un lot de circuits identiques. Pour un grand nombre de circuits intégrés complexes, un contrôle et un déverminage à 100% s'imposent. L'exposé présente les méthodes, les possibilités et les limites de l'essai et du déverminage des circuits intégrés complexes. Il est montré qu'il existe deux limites essentielles: la complexité (nombre d'états et de séquences d'états) et la miniaturisation (nouveaux mécanismes de défaillance).

Mit der Prüfung soll das Qualitäts- und Zuverlässigkeitsniveau einer gegebenen integrierten Schaltung (IC) bestimmt werden. Die Prüfung kann in ihrem Umfang von einer einfachen Eingangskontrolle bis zur Qualifikationsuntersuchung (Freigabeuntersuchung) reichen, die eine Charakterisierung, Umweltund Zuverlässigkeitsprüfungen sowie eine Ausfallanalyse beinhaltet. Die Vorbehandlung soll anderseits den Ausfall aller in einem Los enthaltenen schwachen Komponenten bewirken. Für viele komplexe IC ist eine 100%ige Prüfung und Vorbehandlung notwendig. Der Aufsatz zeigt die Methoden, Möglichkeiten und Grenzen von Prüfung und Vorbehandlung komplexer IC. Zwei wichtige Grenzen sind die Komplexität (Anzahl Zustände und Sequenzen) sowie die Miniaturisierung (neue Ausfallmechanismen).

Cet article est basé sur l'exposé présenté aux Journées d'Electronique 83 de l'EPFL. Il a été préparé pour le compte du *Centre suisse d'essais des composants électroniques (CSEE)*, 22, ruelle Vaucher, 2000 Neuchâtel, une institution de l'ASE. L'auteur était le directeur du CSEE jusqu'à fin juin 1983.

#### Adresse de l'auteur

Dr A. Birolini, ingénieur conseil, chargé de cours EPFZ en assurance qualité et fiabilité, 8606 Nänikon.

#### 1. Introduction

Le développement et l'expansion très rapides de l'électronique au cours de ces dernières années ont été possibles grâce aux progrès réalisés dans la technologie et dans les processus de fabrication des circuits intégrés. En moins de 20 ans, on est passé des circuits SSI/MSI1) avec quelques dizaines de portes aux mémoires de 64 kbit et aux microprocesseurs de 16 bit avec plus de 25 000 portes. Des mémoires à 256 kbit et des microordinateurs à 32 bit avec plus de 100 000 portes sont annoncés. Par leur performance et leur utilisation universelle, les microprocesseurs et les microordinateurs vont influencer fortement les méthodes de développement. L'ingénieur électronicien sera en mesure de réaliser avec quelques circuits intégrés des fonctions très complexes. Les problèmes liés au logiciel, à la sécurité de fonctionnement et à la testabilité vont occuper une place de plus en plus importante.

Dans ce contexte, l'influence de la qualité et de la fiabilité des circuits intégrés complexes sur celles des équipements et systèmes ne fera qu'augmenter. D'autre part, justement par leur complexité et aussi à cause de la forte concurrence sur le marché, la qualité et la fiabilité des circuits intégrés varient fortement d'un fabriquant à l'autre, voire même d'une livraison à l'autre chez le même fabricant. L'expérience montre qu'en moyenne 1 à 3% des circuits LSI/VLSI2) ne remplissent pas entièrement leurs spécifications et, de plus, 1 à 3% de ces composants présentent des défaillances précoces.

Pour tout «équipementier» il se pose donc le problème du choix, de la qualification et du contrôle du niveau de qualité et de fiabilité des circuits intégrés complexes qu'il utilise dans son

SSI = Small Scale Integration

MSI = Medium Scale Integration

LSI = Large Scale Integration

VLSI = Very Large Scale Integration

équipement. C'est un fait connu que les frais de remplacement d'un circuit LSI/VLSI augmentent d'environ un facteur 10 à chaque niveau d'intégration (carte, équipement, système en service).

L'exposé présente les possibilités et limites de l'essai et du déverminage des circuits intégrés complexes et décrit la méthodologie utilisée et les expériences faites.

## 2. Essai électrique des circuits LSI et VLSI

L'essai électrique, ou contrôle d'entrée, a pour but de déterminer si les circuits intégrés délivrés par un fournisseur sont sans défauts. Selon leur importance pour la fiabilité et/ou la sécurité de l'équipement dans lequel ils seront utilisés, on choisit entre un essai à 100% et un essai par échantillonnage. Pour les circuits intégrés complexes, le taux moyen de défauts est en général supérieur à 1%; on préfère alors un essai à 100%. Celui-ci offre aussi les avantages suivants:

- Toutes les fonctions défectueuses, même celles qui ne sont pas utilisées dans l'application prévue, sont décelées.

- 2. Le nombre de réparations au niveau cartes et modules est diminué (souvent de 50-60%).

- Les composants défectueux sont remplacés par le fournisseur, ce qui compense une bonne partie des frais du contrôle d'entrée.

- On est à l'abri des variations du niveau de qualité qui peuvent apparaître d'un lot à l'autre.

- 5. Le contrôle au niveau cartes et modules peut être limité à un essai de fonction.

Même un contrôle d'entrée à 100% ne peut pas garantir que tous les circuits intégrés montés sur une carte soient bons. Un défaut peut avoir été introduit par une fausse manipulation, une surcharge transitoire, une erreur de développement ou de fabrication, etc. Toutefois, le fait d'avoir effectué un contrôle d'entrée à 100% permet d'isoler plus facilement la cause du défaut.

L'essai électrique des circuits intégrés se fait en trois étapes: l'essai de continuité, l'essai de fonction et vérification des paramètres dynamiques (AC), et la vérification des paramètres statiques (DC).

Avec l'essai de continuité on vérifie le chemin entre les broches et les transistors d'entrée ou de sortie du circuit intégré. Pour cela, on connecte toutes les broches à la masse, puis on passe d'une broche à l'autre (en règle générale sans l'alimentation et la masse) en tirant un courant d'environ 100 μA et en mesurant la tension qui s'établit. Pour toutes les entrées et sorties usuelles, cette tension se situe entre -0,1 et -3 V. Le tableau I donne les valeurs mesurées sur un circuit CMOS à 40 broches, dans le cadre d'une caractérisation d'un lot de 20 pièces.

Résultats du test de continuité sur un lot de 20 circuits intégrés CMOS

à 40 broches

Tableau I

25 °C

70 °C

Minimum

-0,48 V

-0,44 V

Moyenne

-0,74 V

-0,64 V

Maximum

-1,12 V

-1,08 V

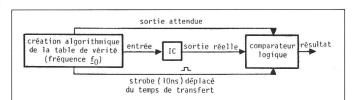

L'essai de fonction est fait en même temps que la vérification des paramètres dynamiques (AC). Le principe est illustré dans la figure 1.

Le générateur délivre à la fréquence f<sub>0</sub> une ligne après l'autre de la partie de la table de vérité que l'on veut vérifier. Pour un circuit à 40 broches actives, par exemple, il s'agit d'un mot binaire de 40 bits, dont 38 varient et 2 (alimentation et masse) restent constants. De ce mot binaire, appelé aussi vecteur de test, les entrées sont appliquées au circuit à tester (IC) et les sorties attendues au comparateur. La comparaison entre les sorties attendues et les sorties réelles (venant du circuit à tester) est faite à un moment bien défini, au moyen d'une impulsion très courte (strobe). Dans le cas d'installations d'essai pour circuits LSI et VLSI, la fréquence fo ainsi que la position du strobe et d'autres impulsions auxiliaires (p.ex. reset) peuvent être variées dans une plage très large. De ce fait, il est possible de vérifier en même temps la table de vérité et la valeur des paramètres dynamiques. Pour les installations actuellement sur le marché, fo atteint 20 MHz et la résolution pour le strobe est de l'ordre de 100 ps.

Un des problèmes fondamentaux dans l'essai de fonction des circuits LSI et VLSI est la création de la table de vérité. Dans le cas général, on re-

Fig. 1 Principe de l'essai de fonction et de la vérification des paramètres dynamiques (AC) pour circuits LSI et VLSI

nonce d'emblée à vouloir vérifier tous les états et séquences d'états possibles, car leur nombre dépasserait rapidement toute grandeur raisonnable. En prenant comme exemple une mémoire avec n cellules et en supposant que chaque cellule constitue un mot, on obtiendrait 2<sup>n</sup> états et n! séquences d'adresses. La table de vérité correspondante aurait alors  $2^n \times n!$  lignes, ce qui correspond à environ  $10^{80}$  pour n =50. La procédure utilisée en pratique consiste à analyser la structure et les régularités de la table de vérité et à trouver un algorithme qui permet de la créer. On se contente donc, le plus souvent, de travailler avec la partie de la table de vérité qui, en considération de l'application prévue ou en s'appuyant sur l'expérience acquise, est jugée suffisante pour l'essai envisagé. Du fait de se contenter d'une partie de la table de vérité, on doit se poser la question de la couverture du test. Ce problème n'est pas encore résolu. Il est lié au problème général de la couverture du test et de la testabilité et est étudié dans plusieurs instituts et laboratoires de recherche [1...8].

Le problème précédent n'existe en général pas pour les circuits SSI et MSI, car il est possible de créer (ligne par ligne) et de charger dans la mémoire locale de l'installation d'essai toute la table de vérité. Pour ces circuits on renonce souvent à la vérification des paramètres dynamiques. Dans ce cas, l'essai peut se faire sur un testeur SSI/MSI, ce qui réduit les coûts de l'essai d'un facteur 2 à 4.

Si on pouvait renoncer aussi pour les circuits LSI et VLSI à la vérification des paramètres dynamiques, on pourrait envisager d'utiliser une méthode d'essai plus simple que celle donnée dans la figure 1; par exemple une des méthodes basées sur le principe de la substitution, de la comparaison ou bien de la simulation des pannes.

La vérification des paramètres DC ne pose aucun problème. Elle se fait sans restrictions, d'après les spécifications du fabricant. Pour cela on utilise une source de courant ou de tension que l'on commute d'une broche à l'autre après avoir conditionné le circuit sur l'état voulu. Dans le premier cas, on force un courant pour mesurer une tension (mesure des tensions de sortie, par exemple  $V_{\rm OH}$  et  $V_{\rm OL}$ ). Dans le deuxième cas, on force une tension pour mesurer un courant (par exemple  $I_{DD}$ ,  $I_{IH}$  et  $I_{IL}$ ). La vérification des paramètres DC est faite souvent à  $V_{\rm DDmin}$ ,  $V_{\rm DDnom}$ ,  $V_{\rm DDmax}$  et au besoin à plusieurs températures (p.ex. 25 et 70 °C). Le tableau II donne des valeurs

Résultats de la mesure de paramètres statiques (DC) sur un lot de 20 circuits intégrés CMOS à 40 broches

Tableau II

|                                                       |                      |                         | 25 °C                   |                         |                         | 70 °C                   |                         |

|-------------------------------------------------------|----------------------|-------------------------|-------------------------|-------------------------|-------------------------|-------------------------|-------------------------|

| $V_{\mathrm{DD}}$                                     |                      | 12 V                    | 15 V                    | 18 V                    | 12 V                    | 15 V                    | 18 V                    |

| $I_{\mathrm{DD}}(\mu\mathrm{A})$                      | min.<br>moy.<br>max. | 310<br>331<br>340       | 410<br>435<br>450       | 560<br>588<br>630       | 260<br>270<br>290       | 340<br>358<br>390       | 470<br>504<br>540       |

| $V_{OH}(V)$<br>( $I_{OH} = -2,4 \text{ mA}$ )         | min.<br>moy.<br>max. | 11,04<br>11,14<br>11,20 | 14,16<br>14,25<br>14,33 | 17,24<br>17,32<br>17,40 | 10,96<br>11,03<br>11,12 | 14,12<br>14,15<br>14,20 | 17,16<br>17,24<br>17,32 |

| $V_{\rm OL}(V)$<br>( $I_{\rm OL} = 2,4 \mathrm{mA}$ ) | min.<br>moy.<br>max. | 0,40<br>0,47<br>0,52    | 0,36<br>0,42<br>0,48    | 0,32<br>0,38<br>0,44    | 0,44<br>0,52<br>0,60    | 0,24<br>0,45<br>0,52    | 0,32<br>0,41<br>0,48    |

| V <sub>Hyst</sub> (V)                                 | min.<br>moy.<br>max. | 2,65<br>2,76<br>2,85    | 3,19<br>3,33<br>3,44    | 3,89<br>3,97<br>4,09    | 2,70<br>2,75<br>2,85    | 3,19<br>3,32<br>3,44    | 3,79<br>3,93<br>4,04    |

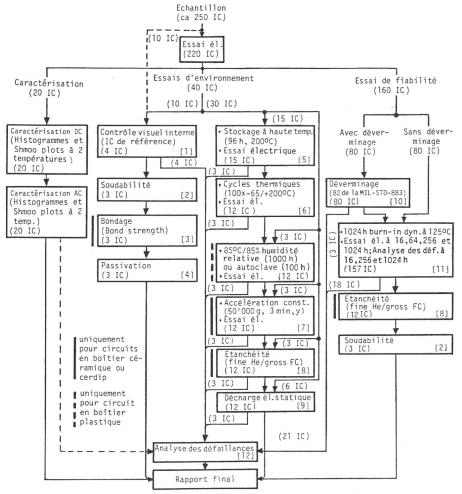

Fig. 2 Procédure de qualification de circuits intégrés pour un niveau de contrainte  $G_F$  et pour  $F\cdot\lambda_1=3\cdot 10^{-5}\,h^{-1}$

(tableau IV, équation 5)

Référence MIL - STD - 883:

[1]/2010.6; [2]/2003.2; [3]/2011.3; [4]/2021; [5]/1008.1-C; [6]/1010.4-C; [7]/2001.2-F; [8]/1014.4-A2-C; [9]/3015.1; [10]/5004.5; [11]/1015.3/1016; [12]/5003

mesurées sur un circuit CMOS à 40 broches dans le cadre d'une caractérisation d'un lot de 20 pièces.

## 3. Essais de qualification des circuits LSI et VLSI

L'essai électrique décrit au paragraphe précédent correspond au contrôle d'entrée effectué à 100% pour vérifier le niveau de qualité des circuits délivrés par un fournisseur. Il ne donne pratiquement aucune information, ni sur les limites du composant lorsqu'il est soumis à des contraintes d'environnement, ni sur son niveau de fiabilité. Pour un ingénieur de développement qui se trouve devant le problème du choix d'un circuit intégré pour une application donnée, les informations venant d'un contrôle d'entrée ne suffisent pas. Ce dont il a besoin, ce sont les

résultats d'un essai de qualification. La figure 2 donne une procédure pour la qualification de circuits intégrés dans le cas où les conditions d'environnement ne dépassent pas celles du matériel fixe au sol (*G*<sub>F</sub> du tableau IV).

La procédure de la figure 2 s'applique surtout aux circuits à la demande. Pour les circuits de grande série, elle peut être réduite en fonction des résultats d'essais semblables dont on dispose.

Après le contrôle d'entrée, la procédure se divise dans les trois branches suivantes: caractérisation, essais d'environnement et essai de fiabilité.

L'analyse des défaillances [10...14], effectuée tout au long de l'essai de qualification, est essentielle pour l'étude des mécanismes de défaillance, la mise en évidence des faiblesses inhérentes et comme base de discussion pour la détermination des actions correctives né-

cessaires pour améliorer la qualité et la fiabilité. Un essai de qualification sans possibilité d'actions correctives chez le fabricant perd une part importante de sa raison d'être, surtout si l'on considère que le coût d'un essai suivant la figure 2 se situe entre fr. 10 000.– et fr. 20 000.–, sans compter le prix du logiciel pour la caractérisation électrique (fr. 2000.– à fr. 20 000.–).

#### 3.1 Caractérisation

La caractérisation est une étude paramétrique expérimentale des caractéristiques électriques du circuit intégré considéré. Elle permet de déterminer l'influence des différents paramètres (tension d'alimentation, niveau d'entrée, fréquence, température, etc.) sur le comportement du circuit. Elle sert de base pour la détermination des points faibles du circuit et pour l'optimisation du logiciel pour le contrôle d'entrée.

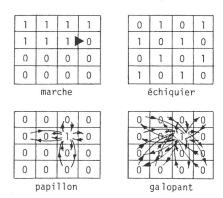

Une caractérisation porte toujours sur l'étude du fonctionnement ainsi que des paramètres statiques (DC) et dynamiques (AC) à deux températures ou plus, selon l'application prévue. Si possible, la caractérisation doit être faite pour différents vecteurs de test. Ceci est surtout vrai pour les mémoires, comme les figures 3 et 4 et le tableau III l'indiquent.

Chaque pattern de la figure 3 met en évidence un ou plusieurs modes de défauts de la mémoire. Une relation qualitative de cette dépendance est donnée dans le tableau III [1]. Des résultats quantitatifs à ce sujet sont peu connus. Du tableau III on peut relever aussi le temps utilisé pour exécuter les différents patterns dans le cas d'une mémoire statique 4 k RAM. La différence entre le temps d'exécution provient essentiellement du fait que ce temps est proportionnel à n pour les 4 premiers patterns, à  $n^{3/2}$  pour les 2 suivants et à

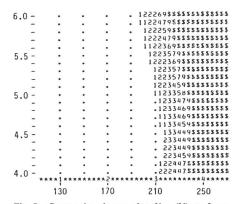

Fig. 3 Exemples de pattern pour mémoires

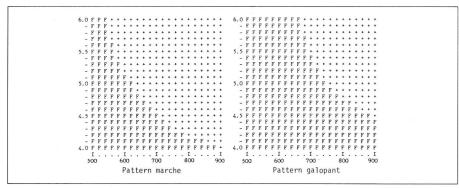

Fig. 4 Shmoo plot de  $V_{DD}$  (V) en fonction du temps d'accès (ns) pour une mémoire statique 1 k RAM (F = failure)

$n^2$  pour les 2 derniers; n étant le nombre de cellules de la mémoire [1; 9]. Pour que le test d'une mémoire RAM soit satisfaisant, il faut exécuter au moins un pattern de type n et un pattern de type  $n^{3/2}$  ou  $n^2$ .

Un outil fondamental pour la caractérisation c'est le «shmoo plot». Il s'agit de la représentation en un système de coordonnées cartésiennes du domaine de fonctionnement d'un circuit intégré donné pour différentes combinaisons de deux paramètres. La figure 4 montre deux exemples pour le cas d'une mémoire statique 1 k RAM [1]. Pour chaque combinaison de la tension d'alimentation et du temps d'accès (p.ex. 5 V et 700 ns), le pattern considéré est exécuté. Si aucune faute n'est trouvée, on indique dans le diagramme une croix, sinon la lettre F.

Pour les shmoo plots de la figure 4 on a donc dû répéter 21×21 = 441 fois le pattern marche et 441 fois le pattern galopant. Une comparaison des deux domaines de fonctionnement montre la différence de sensitivité des deux patterns utilisés. On reconnaît qu'il y a interaction entre les cellules de la même colonne et de la même ligne.

Pour l'interprétation statistique des résultats de la caractérisation, il est avantageux d'élaborer les shmoo plots (fig. 2) non pas sous forme d'histogrammes, mais plutôt sous forme de «composite shmoo plots». Dans un tel composite shmoo plot (fig. 5), le nombre indiqué donne le pourcentage (en pas de 10%) des circuits qui ont fonctionné correctement pour la combinaison choisie des deux paramètres. Pour chaque valeur de l'ordonnée, on peut relever l'allure de la fonction empirique de distribution.

#### 3.2 Essais d'environnement

Le but des essais d'environnement est de vérifier le comportement du circuit intégré dans un environnement défavorable et de déterminer autant que possible ses limites. Il s'agit donc,

Influence des principaux patterns sur le mode de défaut détecté dans l'essai d'une mémoire

| I | at | )I | ea | ıu | 1 | I | I |

|---|----|----|----|----|---|---|---|

|   |    |    |    |    |   |   |   |

| Pattern                | Adres-<br>sage | Décodeur de<br>l'adressage | Perturbation<br>cellules<br>adjacentes | Perturbation<br>colonnes<br>adjacentes | Perturbation<br>lignes<br>adjacentes | Sensibilité<br>aux données | Temps de<br>test mém.<br>RAM 4 k<br>stat. |

|------------------------|----------------|----------------------------|----------------------------------------|----------------------------------------|--------------------------------------|----------------------------|-------------------------------------------|

| Echiquier              |                |                            |                                        |                                        |                                      | *                          | 8 ms                                      |

| Marche                 | **             |                            | *                                      | *                                      |                                      | *                          | 10 ms                                     |

| Cellules adjacentes    |                |                            | **                                     |                                        |                                      |                            | 40 ms                                     |

| Movi                   | **             | *                          | *                                      | *                                      | *                                    | *                          | 168 ms                                    |

| Diagonale<br>galopante | **             | **                         |                                        |                                        | 9                                    |                            | 500 ms                                    |

| Papillon               | *              | *                          | *                                      | **                                     | **                                   |                            | 1 s                                       |

| Trottant               | **             |                            |                                        | *                                      |                                      |                            | 16 s                                      |

| Galopant               | **             | **                         | **                                     | **                                     | **                                   |                            | 32 s                                      |

<sup>\*</sup> bon. \*\* très bon

en règle générale, d'essais semi-destructifs, voire destructifs, pendant lesquels le circuit est sousmis à des sollicitations qui peuvent dépasser les valeurs spécifiées par le fabricant. Une analyse des défaillances après chaque sollicitation est nécessaire pour saisir les mécanismes de défaillance et avoir le suivi d'une dégradation éventuelle.

Le choix de la nature et du niveau de la sollicitation dépend essentiellement de l'application prévue. Dans le cas de la figure 2, on a supposé un environnement allant jusqu'au niveau  $G_F$  du tableau IV. Pour les procédures d'essai, on peut s'appuyer sur des normes [14...17].

Fig. 5 Composite shmoo plot  $V_{DD}$  (V) en fonction du temps d'accès (ns) pour une mémoire statique 4 k RAM (pattern papillon)

Le stockage à haute température, les cycles thermiques, l'accélération constante et l'essai d'étanchéité apparaissent aussi dans la séquence de déverminage et seront décrits au paragraphe 4.

L'essai d'humidité est fait uniquement pour les circuits en boîtier plastique. Son but est d'étudier l'effet de l'humidité sur la surface de la puce, en particulier la corrosion de la métallisation. Pour réduire la durée de l'essai, on opère en même temps à haute température et haute humidité relative. On distingue les deux procédures suivantes:

- 1. Essai à pression normale: 1000 à 2000 h à 85 °C et 85% d'humidité relative. On parle dans ce cas du test 85/85.

- 2. Essai en surpression (autoclave): généralement 100 à 200 h à 121 °C et 100% d'humidité relative (test 121/100).

Il est avantageux de mettre les circuits sous tension pendant environ les deux derniers tiers de l'essai. Cette mise sous tension doit se faire de telle sorte que la consommation du circuit soit minimale (polarisation inverse). Les résultats de l'essai d'humidité devraient servir à déduire le comportement du circuit sous des conditions d'environnement moins sévères. Plusieurs modèles ont été proposés pour le calcul du facteur d'accélération [12; 18...24]. Ces modèles se basent sur l'équation d'Arrhenius et font apparaître dans l'exposant des termes contenant la température et l'humidité. L'utilisation de ces modèles est encore assez difficile. Il ne faut pas non plus oublier que la durée de vie des circuits soumis à l'essai d'humidité est distribuée approximativement d'après une loi de Weibull avec le paramètre  $\beta$ compris entre 1 et 3. Pour une première approximation, on peut dire que d'après les conditions d'utilisation prévues, le facteur d'accélération se situe entre 50 et 500 pour l'essai 85/85 et entre 500 et 5000 pour l'essai 121/100.

L'essai de décharge électrostatique a pour but de vérifier les performances des circuits de protection antistatique. Une procédure utilisée est la suivante:

- 1. On sélectionne 12 circuits bons, 6 au moins venant directement du contrôle d'entrée (fig. 2).

- 2. On partage les 12 circuits en 3 groupes pour l'essai à 1000, 2000 et 3000 V.

- Dans chaque groupe, 2 circuits sont soumis à 5 impulsions positives et 2 circuits à 5 impulsions négatives par rapport à la masse.

- 4. Les impulsions sont créées par la décharge d'un condensateur de 100 à 200 pF en série avec une résistance de 1 à 1,5 k $\Omega$  (inductivité totale <20  $\mu$ H) et espacées de 5 à 10 s.

- 5. Les broches non concernées sont ouvertes.

L'expérience montre qu'un bon circuit de protection doit tenir 1000 V avec 200 pF et 1 k $\Omega$ .

Pour compléter les essais d'environnement, on effectue généralement aussi le contrôle de la soudabilité et la vérification de la résistance des fils de connexion et de l'état de la passivation (fig. 2). La soudabilité ne devrait pas présenter de problèmes, sauf si l'on prévoit de très longues périodes de stockage. Une résistance suffisante des fils de connexions est importante pour les circuits en boîtier céramique ou cerdip. Pour un fil d'A1 de 25 µ, la force de rupture doit être supérieure à 1,5 p. En général, la cassure devrait avoir lieu sur le fil et non à l'un des endroits de fixation. La vérification de l'état de la passivation est importante pour les circuits en boîtier plastique. Des fissures ou pinholes diminuent la résistance à la corrosion. Le contrôle visuel interne (fig. 2) est fait essentiellement pour avoir des spécimens de référence lors de l'analyse des défaillances.

#### 3.3 Essai de fiabilité

Le but de l'essai de fiabilité est de déterminer la valeur et le comportement dans le temps du taux de défaillance. Pour un circuit donné, le taux de défaillance z(t) est égal à la probabilité (référée à  $\delta t$ ) qu'il tombe en panne dans l'intervalle  $(t, t+\delta t)$  étant donné qu'il a survécu jusqu'à l'instant t. Dans le cas général, le taux de défaillance a l'allure de la courbe en baignoire, caractérisée par les périodes des défaillances précoces, aléatoires et d'usure [25...28]. Pendant la période des défaillances aléatoires, le taux de défaillance est sensiblement constant. On pose dans ce cas

$$z(t) = \lambda \tag{1}$$

Pour un circuit avec taux de défaillance constante dès le début, la fonction de fiabilité est donnée par l'expression suivante

$$R(t) = \Pr \left\{ \text{dur\'ee de vie } \tau > t \right\} = e^{-\lambda t}$$

(2)

La valeur moyenne de la durée de vie du circuit est alors

$$E[\text{dur\'ee de vie}] = \frac{1}{\lambda} = MTBF$$

(3)

Pour les circuits intégrés LSI et VLSI, la valeur de  $\lambda$  est comprise entre  $10^{-7}$  et  $10^{-6}$  h<sup>-1</sup>. La détermination expérimentale de  $\lambda$  doit donc se faire au moyen d'un essai accéléré. Pour saisir le mécanisme d'accélération on peut s'appuyer sur les modèles qu'on utilise dans le calcul de la fiabilité prévisionnelle. Ces modèles sont [29...31]:

$$\lambda = \lambda_b \cdot \pi_E \cdot \pi_Q \cdot \pi_A \tag{4a}$$

pour les composants discrets et

$$\lambda = \pi_{\rm O} \left[ C_1 \pi_{\rm T} \pi_{\rm V} + (C_2 + C_3) \pi_{\rm E} \right] \pi_{\rm L} \tag{4b}$$

pour les cicruits intégrés. Parmi les facteurs qui influencent la valeur de  $\lambda$  il faut relever les suivants:

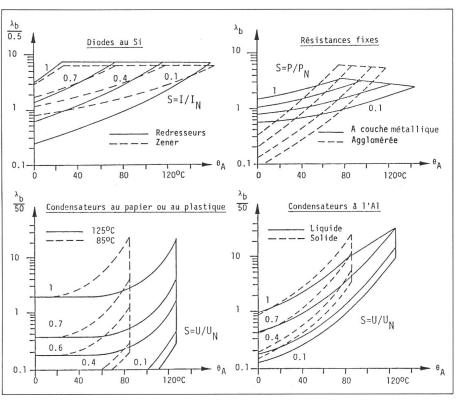

1. Température ambiante. Le taux de défaillance croît en règle générale exponentiellement avec la température. Cette dépendance est considérée dans les facteurs  $\lambda_b$  et  $\pi_T$  des équations 4a et 4b. La figure 6 donne  $\lambda_b$  en fonction de la température ambiante  $\theta_A$  pour différents composants discrets [29]. Pour les circuits intégrés, la

Fig. 6 Facteur  $\lambda_b$  en  $10^{-9}$  h<sup>-1</sup> en fonction de la température ambiante  $\Theta_A$

|                                                 |       |       |        | Paramètres |                      |     |                | Facteur $\pi_{\rm E}$ |            |                      |             |                    |  |

|-------------------------------------------------|-------|-------|--------|------------|----------------------|-----|----------------|-----------------------|------------|----------------------|-------------|--------------------|--|

| Environnement                                   | Vibra | tions | Bruit  | Poussière  | Humidité<br>relative |     | Chocs<br>11 ms | Mon.                  | C<br>Hybr. | Semicon-<br>ducteurs | Résistances | Conden-<br>sateurs |  |

|                                                 | Hz    | g     | dB     |            | %                    | g   | g              |                       |            | discrets             |             |                    |  |

| G <sub>B</sub> sol-favorable<br>(Ground Benign) | 0     | 0     | 40- 70 | faible     | 20- 70               | 0   | 0              | 0,38                  | 0,2        | 1                    | 1.          | 1                  |  |

| G <sub>F</sub> sol-fixe<br>(Ground Fixed)       | 2- 60 | 0,5   | 40- 70 | modéré     | 20- 90               | 0   | 10-15          | 2,5                   | 0,78       | 2,4- 5,8             | 2,4- 2,9    | 1,4- 2,4           |  |

| G <sub>M</sub> sol-mobile<br>(Ground Mobile)    | 2-300 | 0,5-5 | 40-100 | sévère     | 20-100               | 500 | 15-50          | 4,2                   | 2,2        | 7,8–18               | 7,8-11      | 7,8-12             |  |

Fig. 7 Facteur  $\pi_{\Gamma}$  en fonction de la température de jonction  $\Theta_J$

figure 7 donne  $\pi_T$  en fonction de la température de jonction  $\theta_J$  [29].

- 2. Facteur de charge. L'influence du facteur de charge (S dans la fig. 6) est très grande, surtout pour les composants discrets.

- 3. Facteur d'environnement. Les conditions d'environnement sont prises en considération dans le facteur  $\pi_E$ . Le tableau IV résume quelques cas importants et donne les facteurs  $\pi_E$  correspondants [29; 30].

- 4. Déverminage. L'influence du déverminage (et de la qualité de fabrication) est considérée dans le facteur  $\pi_Q$ . Le tableau V donne les valeurs de  $\pi_Q$  pour différents composants électroniques [29].

Des considérations précédentes, on déduit d'une part que la détermination de  $\lambda$  doit tenir compte des conditions réelles de travail du circuit intégré considéré et d'autre part qu'il est possible d'effectuer un essai accéléré en augmentant la température de jonction. La figure 7 montre que le modèle d'Arrhenius peut être utilisé dans ce cas. D'après ce modèle, le facteur d'ac-

célération (F) est donné par l'expression suivante:

$$F = \frac{MTBF_1}{MTBF_2} = \frac{\lambda_2}{\lambda_1} = e^{\frac{E_A}{k} \left(\frac{1}{T_1} - \frac{1}{T_2}\right)} \quad (5)$$

Dans l'équation 5, k est la constante de Boltzmann (8,6·10<sup>-5</sup>eV/K),  $E_A$  l'énergie d'activation et  $\lambda_1$ , respectivement  $\lambda_2$  le taux de défaillance à la température  $T_1$ , respectivement  $T_2$ . L'énergie d'activation varie entre environ

0,4 eV pour TTL en boîtier céramique et 0,9 eV pour CMOS en boîtier plastique (fig. 7).

On est ainsi en mesure de calculer le nombre de circuits que l'on doit soumettre à l'essai de fiabilité (fig. 2). Ce nombre est déterminé à l'aide des équations 4b et 5, de manière à avoir en fin d'essai un nombre attendu de défaillances supérieur ou égal à 5. Dans le cas de la figure 2 on a admis  $F \cdot \lambda_1 = 3 \cdot 10^{-5} \text{ h}^{-1}$ , ce qui donne  $n \approx 160$ .

Facteur  $\pi_Q$  pour différents composants électroniques

Tableau V

| Composant                                                             | Classe    | e, facteurπ <sub>Q</sub> |          |                        |            |               | i            |           |           |

|-----------------------------------------------------------------------|-----------|--------------------------|----------|------------------------|------------|---------------|--------------|-----------|-----------|

| Circuits<br>intégrés<br>monolytiques<br>(MIL-M-38510,<br>MIL-STD-883) | S<br>0,5  | B<br>1                   | B-0<br>2 | B-1<br>3               | B-2<br>6,5 | C<br>8<br>    | C-1   13   _ | D<br>17,5 | D-1<br>35 |

| Circuits<br>intégrés<br>hybrides<br>(MIL-M-38510,<br>MIL-STD-883)     |           | B<br>1                   |          |                        |            |               |              | D<br>60   |           |

| Semi-<br>conducteurs<br>discrets<br>(MIL-S-19500,<br>MIL-STD-750)     |           | JANTXV<br>0,12           |          | <br>  JAN<br>  1,2<br> | Lower<br>6 | Plastic<br>12 | -            |           |           |

| Résistances<br>(MIL-STD-199,<br>MIL-STD-202)                          | S<br>0,03 | R<br>0,1                 | P<br>0,3 | M<br>  1               | NE<br>5    | Lower<br>15   |              |           |           |

| Condensateurs<br>(MIL-STD-198,<br>MIL-STD-202)                        | S<br>0,03 | R<br>0,1                 | P<br>0,3 | M<br>  1               | L<br>1,5   | NE<br>3       | Lower        |           |           |

Le déverminage n'est pas effectué à droite de la ligne pointillée

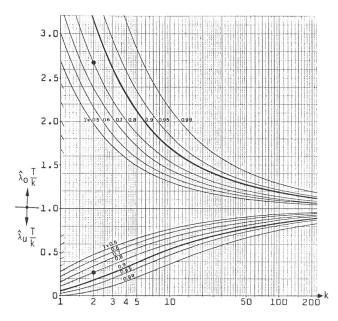

Fig. 8

Limites de confiance  $\hat{\lambda}_{\mathbf{u}}$  et  $\hat{\lambda}_{\mathbf{o}}$  T temps cumulé de test k nombre de défaillances dans T  $\gamma$  niveau de confiance

Exemple:  $T = 10^6 \text{ h}, k = 2$ ,  $\gamma = 0.8$  donne l'intervalle  $[0.56, 5.3] \, 10^{-6} \, \text{h}^{-1}$

Une fois l'essai de fiabilité terminé, on peut évaluer le taux de défaillance observé. Si T est le temps cumulé de test et k le nombre de défaillances aléatoires observées dans T, on obtient pour l'estimation ponctuelle de  $\lambda$  la valeur

$$\hat{\lambda} = k/T \tag{6}$$

L'estimation par intervalle peut être faite directement à l'aide de la figure 8 [25].

Dans la procédure de la figure 2, la branche avec déverminage a été introduite pour pouvoir estimer le facteur de qualité ( $\pi_Q$  dans l'équation 4b). Les essais d'étanchéité et de soudabilité à la fin de l'essai de fiabilité sont effectués pour détecter une dégradation éventuelle. Il est, en général, accepté qu'après 1000 h de burn-in, la soudabilité soit plus ou moins détruite.

Séquences de déverminage pour circuits intégrés

Tableau VI

| Séquence                   | 8                                        | Classe                                  |                 |

|----------------------------|------------------------------------------|-----------------------------------------|-----------------|

| Sequence                   | S                                        | В                                       | С               |

| Connexions                 | 100%                                     | _                                       | _               |

| Contrôle visuel interne    | 100%                                     | 100%                                    | 100%            |

| Stockage à haute           |                                          |                                         | 10070           |

| température                | 24 h/150 °C                              | 24 h/150 °C                             | 24 h/150 °C     |

| Cycles thermiques          | $10 \times -65 / + 150 ^{\circ}\text{C}$ | $10 \times -65 / +150 ^{\circ}\text{C}$ | 10× -65/+150 °C |

| Accélération const.        | 30 000 g/60 s                            | $30000\mathrm{g}/60\mathrm{s}$          | 30 000 g/60 s   |

| Etanchéité (fine/gross.)   | 100%                                     | 100%                                    | 100%            |

| Détection de particules    | 100%                                     |                                         | -               |

| Essai électrique réduit    | 100%                                     |                                         | -               |

| HTRB (stock. à haute temp. |                                          |                                         |                 |

| avec pol. inv.)            | 72 h/150 °C                              | _                                       | -               |

| Essai électrique réduit    | 100%                                     | 100%                                    | -               |

| Burn-in                    | 240 h/125 °C                             | 160 h/125 °C                            | -               |

| Essai électrique           | 100%                                     | 100%                                    | 100%            |

| Rayons X                   | 100%                                     | -                                       | -               |

| Contrôle visuel externe    | 100%                                     | 100%                                    | 100%            |

### Distribution typique des modes de défaillance dans les circuits intégrés

Tableau VII

| Mode de défaillance    | Stokage à hau | te température | Cycles th | ermiques    | Accélération | Bur   | n-in |

|------------------------|---------------|----------------|-----------|-------------|--------------|-------|------|

|                        | céram.        | plast.         | céram.    | plast.      | const.       | stat. | dyn. |

| Fil de connexion       |               |                | 2%        | 17%         | 10%          | 2%    | 13%  |

| Adhérence de la puce   |               |                | 270       | 1770        | 15%          | 270   | 137  |

| Diffusion              |               |                |           |             | 1370         | 7%    | 3%   |

| Boîtier                |               |                | 74%       |             | 55%          | 2%    | 5%   |

| Contact bond puce      | 23%           | 33%            | 4%        | 57%         | 20%          | 11%   | 12%  |

| Métallisation          |               |                |           | 5 (6)(8)(6) |              |       |      |

| (corrosion,            |               |                |           |             |              |       |      |

| électromigration)      |               |                | 7%        | 11%         |              | 24%   | 21%  |

| Surface (contamination |               |                |           |             |              |       |      |

| ionique, particules)   | 60%           | 56%            | 2%        |             |              | 11%   | 22%  |

| Oxide (pinholes,       |               |                |           |             |              |       |      |

| passivation)           | 17%           | 11%            | 7%        | 9%          |              | 43%   | 14%  |

| Substrat               |               |                | 4%        | 6%          |              |       | 10%  |

|                        |               |                | -         |             |              |       |      |

|                        | 100%          | 100%           | 100%      | 100%        | 100%         | 100%  | 100% |

## 4. Déverminage des circuits LSI et VLSI

Le contrôle d'entrée est un essai de courte durée, ne dépassant en général pas 5 ou 10 s. Il permet donc de vérifier uniquement l'état de fonctionnement momentané du circuit en question. L'expérience montre qu'en moyenne 1 à 3% des circuits LSI/VLSI ont des défaillances précoces. Une méthode bien établie pour provoquer les défaillances précoces est de soumettre les circuits à un déverminage. Le tableau VI donne les séquences de déverminage selon la norme militaire MIL-STD-883 [14]. Chaque sollicitation y active un ou plusieurs mécanismes de défaillance. Le tableau VII montre la distribution typique des modes de défaillance dans les circuits intégrés [35].

Quant à la distribution des défaillances précoces, on peut utiliser pour les circuits en boîtier céramique les valeurs indicatives suivantes: stockage à haute température 0 à 5%, cycles thermiques 5 à 10%, accélération constante 0 à 5%, étanchéité 10 à 15%, burn-in 70 à 80%.

Pour un petit ou moyen utilisateur de circuits intégrés, il n'est pas possible d'effectuer le contrôle visuel interne ni d'exercer une grande influence sur les procédures d'assurance qualité du fabricant. Avec le déverminage, on peut donc atteindre au maxi-

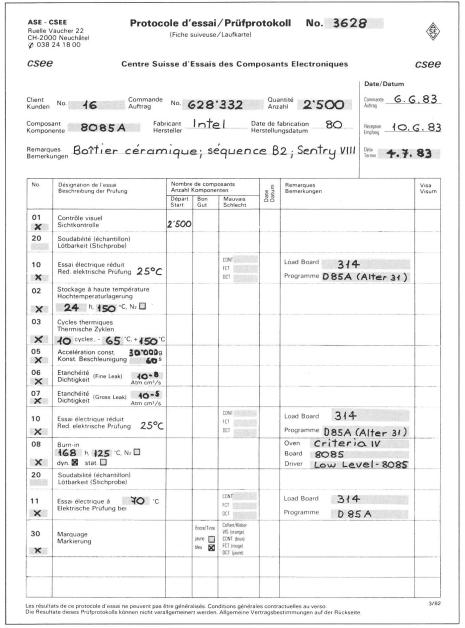

Fig. 9 Protocole d'essai, resp. fiche suiveuse du CSEE

Une telle fiche est établie avant le début d'un contrôle et déverminage complet (classe B2 de la MIL - STD - 883) de circuits intégrés en boîtier céramique.

mum la classe B2 de la MIL-STD-883 [14; 29]. Un exemple de la séquence correspondante est donnée à la figure 9. Les différents pas de la séquence de déverminage sont:

#### 4.1 Contrôle visuel externe

Le contrôle visuel externe fait ressortir tous les défauts externes du boîtier (fissures, cassures, déplacements), des broches (dimensions, intégrité, oxydation) et de l'impression. Il est effectué en partie au commencement et en partie à la fin de chaque séquence d'essai.

#### 4.2 Stockage à haute température

Le but du stockage à haute température est de stabiliser l'équilibre thermodynamique et, de ce fait, les caractéristiques électriques du circuit. Il active aussi les mécanismes de défaillance liés aux problèmes de surface (contamination ionique, particules), de contact fil-puce et de défauts dans la passivation ou dans l'oxyde. Pour le stockage à haute température, les circuits intégrés sont posés sur une plaque métallique (avec les broches sur la plaque) et placés pendant 24 h dans un four à 150 °C. En cas de problèmes avec la soudabilité, le stockage à haute

température peut se faire en atmosphère protégée ( $N_2$ ).

#### 4.3 Cycles thermiques

Le but des cycles thermiques est de vérifier la capacité des circuits de supporter des changements rapides de température. Ils font ressortir en particulier les problèmes liés à la différence des coefficients de dilatation des matériaux en contact. Ils activent aussi les mécanismes de défaillance dans la métallisation, l'oxyde et le substrat. Les cycles thermiques sont exécutés dans un four à deux ou trois chambres (air/ air), entre lesquelles se déplace un ascenseur. Les circuits sont posés sur une plaque en métal (avec les broches sur la plaque) et soumis à 10 cycles entre -65 et +150 °C. Le temps d'attente aux températures extrêmes est de 10 min et le temps de transfert maximum de 5 min. En cas de problèmes avec la soudabilité, les cycles thermiques peuvent se faire en atmosphère protégée (N2).

#### 4.4 Accélération constante

Le but de l'accélération constante est de vérifier l'adhérence de la puce au support et la résistance mécanique du boîtier, des fils de connexion et des contacts fil-puce et fil-broche. Elle est exécutée uniquement pour les boîtiers céramiques, cerdips ou métalliques. Les circuits sont placés dans une centrifugeuse et soumis à une accélération de 30 000 g pendant 60 s.

#### 4.5 Etanchéité

Le but de l'essai d'étanchéité est de vérifier que la cavité autour de la puce soit suffisamment étanche. Il est exécuté uniquement pour les boîtiers céramiques, cerdips et métalliques. L'essai commence avec la mesure fine (fine leak). Les circuits sont placés sous vide (1 h à 0,5 mm Hg) et puis pendant 20 h dans de l'hélium à 5 atm. Après un temps d'attente d'environ 30 min à l'air, les circuits sont passés dans un spectromètre de masse qui détecte les fuites d'He. La sensibilité est de l'ordre de 10<sup>-8</sup> atm cm<sup>3</sup>/s. La mesure grossière (gross leak) est faite après le mesure fine. Les circuits sont mis sous vide (1 h à 5 mm Hg), puis pendant 3 h dans du fluorcarbone FC-72 à 5 atm. Après un temps d'attente d'environ 2 min à l'air, les circuits sont passés dans un bain indicateur contenant du fluorcarbone FC-40 à 125 °C. La fuite de FC-72 est observée pendant 30 s

| Taux | movens  | de | défaut | et d | e défaillance |  |

|------|---------|----|--------|------|---------------|--|

| Idux | HIUAGHS | ue | uelaut | elu  | e delamance   |  |

|             |                                      | Taux moyens | Nombre  | ombre Lots avec |      | Distribution selon le genre de défaut |      |           |        |  |  |  |

|-------------|--------------------------------------|-------------|---------|-----------------|------|---------------------------------------|------|-----------|--------|--|--|--|

| Composantis | Composants Nombre d'ICs de défaut et |             | de lots | déverminage **) | CONT | FCT                                   | DCT  | non prog. | autres |  |  |  |

| TTL         | 964'837                              | 0,4 %       | 894     | 59 %            | 5 %  | 55 %                                  | 37 % | _         | 3 %    |  |  |  |

| CMOS        | 553'119                              | 1,5 %       | 715     | 70 %            | 5 %  | 15 %                                  | 75 % | _         | 5 %    |  |  |  |

| PMOS        | 390'500                              | 1,6 %       | 85      | 96 %            | 3 %  | 78 %                                  | 15 % | _         | 4 %    |  |  |  |

| μP/Periph.  | 713'658                              | 1,6 %       | 1'014   | 20 %            | 4 %  | 81 %                                  | 14 % | _         | 1 %    |  |  |  |

| RAM         | 173'264                              | 1,4 %       | 230     | 32 %            | 7 %  | 59 %                                  | 30 % | _         | 4 %    |  |  |  |

| EPROM       | 181'119                              | 2,8 %       | 312     | 98 %            | 3 %  | 43 %                                  | 16 % | 37 %      | 1 %    |  |  |  |

| Linear      | 61'623                               | 2,2 %       | 103     | 75 %            | -    | _                                     | 96 % | _         | 4 %    |  |  |  |

| Total       | 3'038'120 *)                         | 1,3 %       | 3'353   | 53 %            | 4 %  | 55 %                                  | 34 % | 5 %       | 2 %    |  |  |  |

\*\*) Principalement stockage à haute température et cycles thermiques

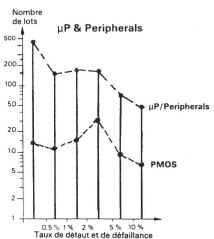

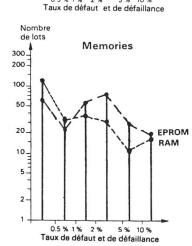

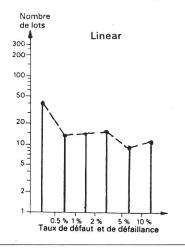

#### Nombre de lots en fonction des classes du taux de défaut et de défaillance

Fig. 10 Résultats d'essais au CSEE dans la période de juin 1980 à juin 1983

(bulles). La sensibilité est de l'ordre de  $10^{-5}$  atm cm<sup>3</sup>/s.

#### 4.6 Burn-in

Le burn-in est cher mais efficace. Il fait ressortir entre 70 et 80% des défaillances précoces. Dans le burn-in, les circuits intégrés sont alimentés et travaillent dans un four à la température de 125 °C. On distingue entre burn-in statique, souvent en polarisation inverse, et burn-in dynamique, où les entrées sont activées par des signaux variables et les sorties sont chargées. Comme il résulte aussi du tableau VII,

le burn-in statique fait apparaître surtout les problèmes d'oxyde et de métallisation. Le burn-in dynamique, par contre, agit assez uniformément sur tous les mécanismes de défaillances. L'expérience montre que pour les circuits LSI et VLSI, le burn-in dynamique est d'un facteur 1,5 à 3 plus efficace que le burn-in statique. Cet avantage s'explique aussi par le fait que, dans le burn-in dynamique, toutes les parties du circuit travaillent. En cas de problèmes avec la soudabilité, le burn-in peut se faire en atmosphère protégée ( $N_2$ ). Le facteur d'accéléra-

tion introduit par le burn-in se calcule avec l'équation (5). Si l'on considère que ce facteur est souvent compris entre 30 et 150, on arrive à la conclusion que pour couvrir une période de défaillances précoces d'environ 3000 h, un burn-in entre 20 et 100 h suffit. Ce résultat explique le choix du CSEE de fixer à 72 h la durée standard du burn-in au lieu des 160 h fixées par la MIL-STD-883.

#### 5. Expériences

Les résultats de nombreux essais et déverminages montrent que le taux moyen de défauts des circuits intégrés LSI et VLSI varie entre 1 et 3% et, de plus, 1 à 3% de ces composants présentent des défaillances précoces [35...37]. Les résultats obtenus au CSEE dans la période juin 1980 à juin 1983 sont donnés dans la figure 10. Il en résulte que les taux de défauts et de défaillances des mémoires (RAM et EPROM) et des circuits linéaires varient très fortement. Une grande variation a été observée aussi d'un lot à l'autre chez le même fournisseur.

Les expériences faites au CSEE dans le contrôle, le déverminage et la qualification de circuits intégrés complexes peuvent se résumer ainsi:

- 1. Le développement et la maintenance du logiciel pour l'essai électrique et la caractérisation des circuits LSI et VLSI est très onéreux. Pour qu'un centre comme le CSEE soit efficace, il faut un groupe de 4 à 6 ingénieurs à temps plein.

- 2. Le développement des boards et des cartes de contrôle pour le burn-in dynamique demande une grande expérience. Au CSEE il a fallu quatre hommes années pour atteindre le standard voulu.

- 3. L'essai électrique et le déverminage doivent se faire d'une façon sélective et tenir compte de l'application prévue.

- 4. Un essai électrique et un déverminage à 100% s'imposent pour les mémoires et pour les circuits à la demande.

- 5. Les procédures de qualification et de déverminage doivent être continuellement renouvelées et complétées (nouveaux mécanismes de défaillances à cause de nouvelles technologies). L'analyse physico-chimique des défaillances est indispensable. La figure 11 montre quelques résultats de ces analyses. Obtenues au CSEE en collaboration avec le FSRM et le CEH à Neuchâtel.

#### a

d

b

#### Fig. 11 Exemples d'analyse physico-chimique de défaillances

- a fissures dans la passivation

- Al-Si «over alloying» sous une fenêtre de contact

- c mauvais alignement de masques

- d mauvais recouvrement d'une marche (Photos CEH)

#### **Bibliographie**

- W.G. Fee: Memory testing. Compcon 77 Spring. Tutorial: LSI Testing, San Francisco/California. New York, IEEE, 1978; p. 81...88.

T.W. Williams and K.P. Parker: Design for testability—a survey Proc. IEEE 71(1983)1, p. 98...112.

E.J. McCluskey: Design for autonomous test. 1980 IEEE Test Conference: Testing for the 80's. Philadelphia, 11...13 November 1980. Digest of papers, paper No. 2.1, p. 15...21.

K. Muranaga: Statistical and practical aspects of

- [4] K. Muranaga: Statistical and practical aspects of testing LSI and VLSI devices. 1980 IEEE Test Conference: Testing for the 80's. Philadelphia, 11...13 November 1980. Digest of papers, paper No. 11.1, p. 289...294.

- [5] G.H. Bell: Test generation for LSI. A menu of methodologies. Proceedings of the Annual IEEE Reliability and Maintainability Symposium 1980, p. 239...241.

- G. Saucier: Les perspectives dans le domaine du test et de la testabilité des circuits à très haute intégration. Rapport de recherche IMAG No. 268. Grenoble, Laboratoire IMAG, 1981.

- [7] G. Sauciere.a.: Le test et la testabilité des circuits intégrés. Journées d'Electronique 1983. Lausanne, Ecole Polytechnique Fédérale, 11...13 octobre 1983; p. 27, 27, 27.

- [8] R.W. Comerford and J. Lyman: Self-testing. Special report. Electronics –(1983)March 10, p. 109...124.

[9] M. Marshall: Through the memory cells. Further explorations of IC's in Testingland-2. EDN 21(1976)4, p. 77...85.

- [10] Microelectronic failure analysis techniques: A procedural guide. MFAT-1. New York, Reliability Analysis Center/Griffis Air Force Base, 1981.

- J.R. Shappirio and C.F. Cook: Modern analytical techniques for failure analysis. Solid-State Technology 22(1979)9, p. 89...94.

D. Gerth u.a.: Prüfmethoden. Landis und Gyr Mitt. 29(1982)1, S. 10...26.

- 25(152)1(3. to...20. F. Fantini a.o.: Failure mechanisms and analysis of VLSI-ICs. Journées d'Electronique 1983. Lausanne, Ecole Polytechnique Fédérale, 11...13 octobre 1983; p. 85...104.

- Test methods and procedures for microelectronics. MIL-Standard 883, edition B, 1977.

- Test methods for semiconductor devices. MIL-Standard 750, edition B, 1970.

- Test methods for electronic and electrical parts. MIL-Standard 202, edition F, 1980.

- Essais fondamentaux climatiques et de robustesse mécanique. Publications de la CEI 68-2-1...68-2-48, 1960...1982.

- [18] N. Lycondes: The reliability of plastic microcircuits in moist environments. Solid-State Technology in moist environments. 21(1978)10, p. 53...62.

- 21(19/8)10, p. 53...62.

S.P. Sim and R.W. Lawson: The influence of plastic encapsulants and passivation layers on the corrosion of thin aluminium films subjected to humidity stress. Proceedings of the 17th Annual IEEE Symposium on Reliability Physics 1979, p. 103...112.

W.J. McGarvey: Autoclave vs. 85 °C/85% R.H. testing.—A comparison. Proceedings of the 17th Annual IEEE Symposium on Reliability Physics 1979, p. 136. 142

- [21] D. Ströhle: Feuchteprobleme bei LSIs. NTG-Fachtagung «Grossintegration», Baden-Baden, 16...18. 3. 1981. NTG-Fachberichte 77(1981), S. 106...109.

- K.M. Striny and A.W. Schelling: Reliability evalua-tion of aluminium-metallized MOS dynamic RAMs in plastic packages in high humidity and temperature environments. IEEE Trans. CHMT 4(1981)4, p.

- [23] T. Yoshida, T. Takahashi and S. Koyama: A new accelerated test method for moisture resistance of plastic encapsulated LSIs. Proceedings of the 20th Annual IEEE Symposium on Reliability Physics 1982, p. 268...271.

- D. Ströhle: Zuverlässigkeit von plastikverkapselten LSIs bei intermittierendem Betrieb. NTG-Fachta-gung «Grossintegration», Baden-Baden, 7...9. März 1983. NTG-Fachberichte 82(1983), S. 91...96.

- [25a] A. Birolini: Zuverlässigkeit von Schaltungen und Systemen. Autographie zur Vorlesung an der ETH Zürich. 5. Auflage. Zürich, Selbstverlag, 1983.

- [25b] A. Birolini: Technique de la fiabilité. Cours d'appli-cation à l'Université de Neuchâtel, 2<sup>e</sup> édition. Zurich,

- édité par l'auteur, 1983.

[25c] A. Birolini: Qualität und Zuverlässigkeit technischer Systeme: Theorie, Praxis, Management. Berlin, Springer-Verlag, im Druck.

- [26] M. Schwob et G. Peyrache: Traité de fiabilité. Paris, Masson, 1969.

- Development guide for reliability. Part 1 to 6. AMC Pamphlet 706–195...706–200. Alexandria/VA, Head-quarters, US Army Material Command, 1975/1976.

- R.T. Anderson a.o.: Reliability design handbook RDH-376. New York, Reliability Analysis Center/ Griffis Air Force Base, 1976.

- Reliability prediction of electronic equipment. MIL-Handbook 217, edition D, 1982.

- [30] Recueil de données de fiabilité. Lannion, Centre National d'Etudes des Télécommunications (CNET), 1976/1982.

- [31] F.H. Reynolds: Measuring and modelling integrated circuit failure rates. In: Reliability in electrical and electronic components and systems. Fifth European Conference on Electrotechnics—Eurocon '82. Co-penhagen/Denmark, June 14...18, 1982, p. 32...45.

- pennägen/ Denmärk, June 14...18, 1962, p. 32...45.

[32] Reliability design qualification and production acceptance tests: Exponential distribution. MIL-Standard 781, edition C, 1977.

[33] A. Birolini: Möglichkeiten und Grenzen der Qualifikation, Prüfung und Vorbehandlung integrierter Schaltungen. Qualität und Zuverlässigkeit 27(1982)11, S. 321...326.

[34] D. B. Berles et Schelberted testing hyndbook. Porto.

- D.S. Peck a.o.: Accelerated testing handbook. Portola-Valley/California, Technology Associated, 1981.

- H.C. Rickers: Microcircuit screening effectiveness. TRS-1. New York, Reliability Analysis Center/Griffis Air Force Base, 1978.

- B.P. Davis: Untersuchungen der Wirtschaftlichkeit automatischen Testens elektronischer Bauelemente und Baugruppen. Handbuch automatisches Testen. Band I. Haar bei München, Verlag Markt und Tech-

- Band 1. Haar bet Mulicien, Verag Maria Carlinik, 1981.

M.C. Berger: Expérience pratique de déverminage de composants électroniques. Microelectronics and Reliability 22(1982)4, p. 671...680.